- 您现在的位置:买卖IC网 > Sheet目录450 > ISL5216EVAL1 (Intersil)EVALUATION BOARD FOR ISL5216KI

�� �

�

�

�ISL5216�

�Back� End� Data� Routing�

�MAG:� I�

�PATH� 0�

�AGC�

�LOOP�

�FILTER�

�PATH� 1�

�dphi/dt:� Q�

�I1�

�Q1�

�MUX�

�GAIN�

�x1,� x2�

�MAG�

�(4:0)�

�x4,� x8�

�FROM�

�CIC�

�M�

�U�

�X�

�FILTER�

�COMPUTE�

�ENGINE�

�FIFO/�

�TIMER�

�AGC�

�MULT�

�CART�

�TO�

�POLAR�

�SHIFT�

�d/dt�

�M�

�U�

�X�

�PHASE�

�I2�

�PATH� 3�

�Q2�

�PATH� 2�

�I2�

�Q2�

�EXT� AGC�

�GAIN�

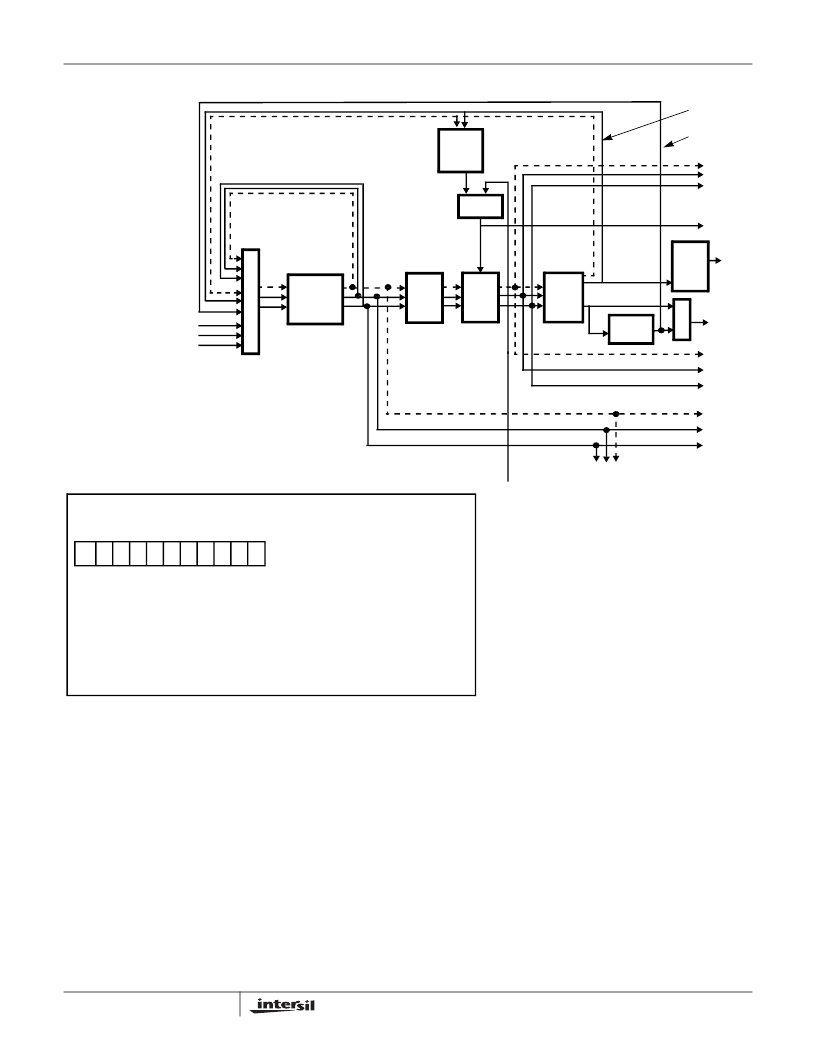

�DESTINATION� BIT� MAP�

�(BITS� 28:18� OF� FIR� INSTRUCTIONS� BIT� FIELD)�

�28�

�28�

�27�

�27� 26� 25� 24� 23� 22� 21� 20� 19� 18�

�AGC� LOOP� GAIN� SELECT� (PATH� 01� ONLY)�

�UPDATE� AGC� LOOP� (PATH� 01� ONLY)�

�26,� 25�

�24�

�23�

�22:18�

�PATH� 00� -� -� IMMEDIATE� FILTER� PROCESSOR� FEEDBACK� PATH�

�01� -� -� FIFO/AGC� PATH� TO� I1� AND� Q1�

�10� -� -� DIRECT� OUT/CASCADE� PATH� TO� I2� AND� Q2�

�11� -� -� FIFO/AGC� PATH� TO� I2� AND� Q2�

�STROBE� OUTPUT� SECTION� (START� SERIAL� OUTPUT� WITH� THIS� SAMPLE)�

�FEED� MAG/PHASE� BACK� TO� FILTER� PROCESSOR�

�FILTER� PROCESSOR� SEQUENCE� STEP� NUMBER�

�Back� End� Section�

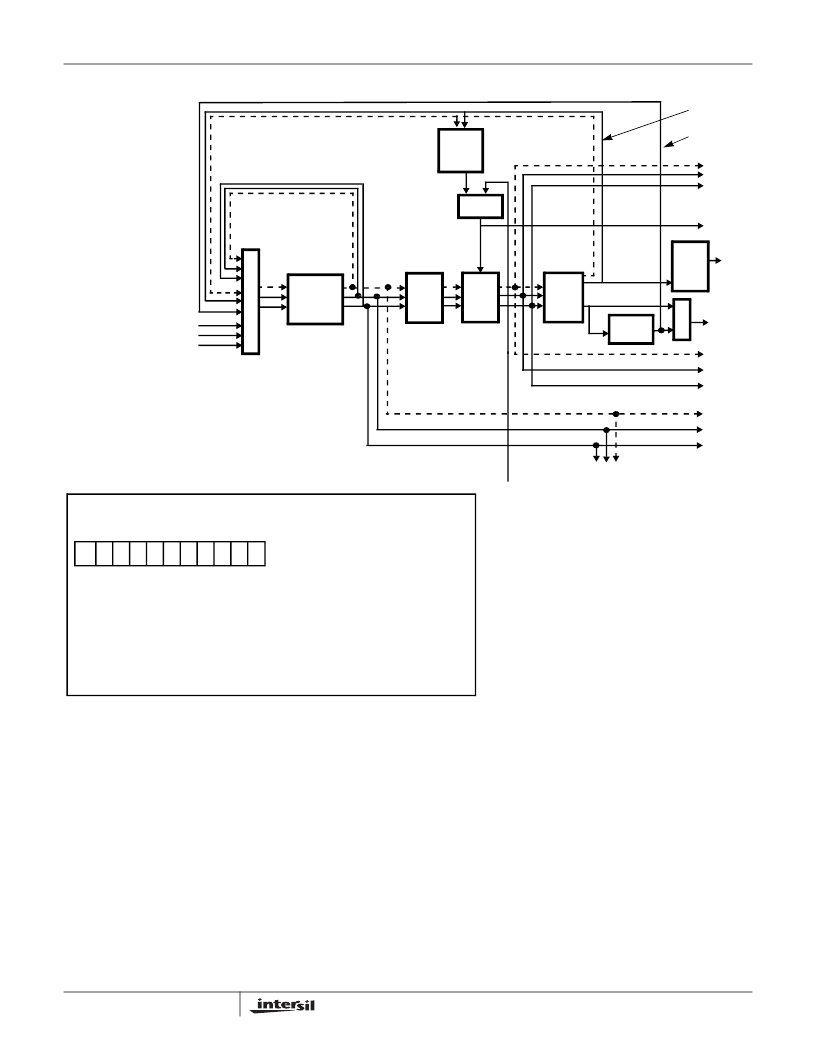

�One� back-end� processing� section� is� provided� per� channel.�

�Each� back� end� section� consists� of� a� filter� compute� engine,� a�

�FIFO/timer� for� evenly� spacing� samples� (important� when�

�implementing� interpolation� filters� and� resamplers),� an� AGC�

�and� a� cartesian-to-polar� coordinate� conversion� block.� A�

�block� diagram� showing� the� major� functional� blocks� and� data�

�routing� is� shown� above.� The� data� input� to� the� back� end�

�section� is� through� the� filter� compute� engine.� There� are� two�

�other� inputs� to� the� filter� compute� engine,� they� are� a� data�

�recirculation� path� for� cascading� filters� and� a� magnitude� and�

�d� φ� /dt� feedback� path� for� AM� and� FM� filtering.� There� are� seven�

�outputs� from� each� back� end� processing� section.� These� are� I�

�and� Q� directly� out� of� the� filter� compute� engine� (I2,� Q2),� I� and�

�13�

�Q� passed� through� the� FIFO� and� AGC� multipliers� (I1,� Q1),�

�magnitude� (MAG),� phase� (or� d� φ� /dt),� and� the� AGC� gain�

�control� value� (GAIN).� The� I2/Q2� outputs� are� used� when�

�cascading� back� end� stages.� The� routing� of� signals� within� the�

�back� end� processing� section� is� controlled� by� the� filter�

�compute� engine.� The� routing� information� is� embedded� in� the�

�instruction� bit� fields� used� to� define� the� digital� filter� being�

�implemented� in� the� filter� compute� engine.�

�FN6013.3�

�July� 13,� 2007�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL5217EVAL1

EVALUATION BOARD FOR ISL5217KI

ISL5239EVAL1

EVALUATION BOARD FOR ISL5239

ISL5239KIZ

IC LINEARIZER PRE-DISTORT 196BGA

ISL5416EVAL1

EVALUATION PLATFORM FOR ISL5416

ISL55005IEZ-T7

IC AMP MMIC BIPO BROADBND SC70-6

ISL55007IEZ-T7

IC AMP MMIC BIPO BROADBND SC70-6

ISL55008IEZ-T7

IC AMP MMIC BIPO BROADBND SC70-6

ISL55009IEZ-T7

IC AMP MMIC BIPO BROADBND SC70-6

相关代理商/技术参数

ISL5216KI

功能描述:上下转换器 QUAD DIGITAL DOWNCONVERTER,IND TEMP,0.8M RoHS:否 制造商:Texas Instruments 产品:Down Converters 射频:52 MHz to 78 MHz 中频:300 MHz LO频率: 功率增益: P1dB: 工作电源电压:1.8 V, 3.3 V 工作电源电流:120 mA 最大功率耗散:1 W 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-128

ISL5216KI-1

功能描述:上下转换器 QUAD DIGITAL DOWNCONVERTER,IND TEMP,1.OMM PITCH BGA PACKAG RoHS:否 制造商:Texas Instruments 产品:Down Converters 射频:52 MHz to 78 MHz 中频:300 MHz LO频率: 功率增益: P1dB: 工作电源电压:1.8 V, 3.3 V 工作电源电流:120 mA 最大功率耗散:1 W 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-128

ISL5216KI-1Z

功能描述:上下转换器 W/ANL QD DIG DWNCNVRTR 1 OM PITCH RoHS:否 制造商:Texas Instruments 产品:Down Converters 射频:52 MHz to 78 MHz 中频:300 MHz LO频率: 功率增益: P1dB: 工作电源电压:1.8 V, 3.3 V 工作电源电流:120 mA 最大功率耗散:1 W 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-128

ISL5216KIZ

功能描述:上下转换器 W/ANNEAL QD DIGTL DWNCNVRTR IND TEMP RoHS:否 制造商:Texas Instruments 产品:Down Converters 射频:52 MHz to 78 MHz 中频:300 MHz LO频率: 功率增益: P1dB: 工作电源电压:1.8 V, 3.3 V 工作电源电流:120 mA 最大功率耗散:1 W 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-128

ISL5217

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Quad Programmable Up Converter

ISL5217_05

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Quad Programmable Up Converter

ISL5217EVAL1

功能描述:EVALUATION BOARD FOR ISL5217KI RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:- 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

ISL5217KI

功能描述:上下转换器 196BGA,-40+85C PROGRAMMABLE QUAD UP CONVERTER RoHS:否 制造商:Texas Instruments 产品:Down Converters 射频:52 MHz to 78 MHz 中频:300 MHz LO频率: 功率增益: P1dB: 工作电源电压:1.8 V, 3.3 V 工作电源电流:120 mA 最大功率耗散:1 W 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PQFP-128